Samsung’s new 2 nm foundry process to cut chip size by 17%

Intel is tipped to become the first chipmaker to apply the backside power delivery network to the 2-nanometer node

By Aug 22, 2024 (Gmt+09:00)

Samsung steps up AR race with advanced microdisplay for smart glasses

When in S. Korea, it’s a ritual: Foreigners make stops at CU, GS25, 7-Eleven

Maybe Happy Ending: A robot love story that rewrote Broadway playbook

NPS yet to schedule external manager selection; PE firms’ fundraising woes deepen

US auto parts tariffs take effect; Korea avoids heavy hit

A new contract chipmaking technology, dubbed the backside power delivery network (BSPDN), will reduce the size of a 2-nanometer chip by 17%, compared with the traditional front-end power delivery technology, said Samsung Electronics Co.'s foundry business executive on Thursday.

The BSPDN, which Samsung is set to apply for mass production of the 2 nm process from 2027, also improves performance and power efficiency by 8% and 15%, respectively, compared to the chips with the front-end power delivery networks, said Lee Sungjae, vice president and Foundry PDK Development Team at Samsung.

He outlined the technological prowess of BSPDN in a keynote speech at Siemens EDA Forum 2024. It was the first time for a Samsung foundry business executive to give a detailed account of its BSPDN technology in public.

BSPDN is called a next-generation chip foundry technology. It places power rails on the back of the semiconductor wafer to eliminate bottlenecks between the power and signal lines, allowing for smaller chips.

Contract chipmakers are gearing up to adopt the advanced chipmaking process. Leading the pack, Intel plans to produce chips with BSPDN on the Intel 20A process, known as a 2 nm node, within the year. It dubbed its BSPDN technology as PowerVia.

TSMC, which controls 62% of the global foundry market, said it plans to introduce the BSPDN to its 1.6 nm and below process nodes around the end of 2026.

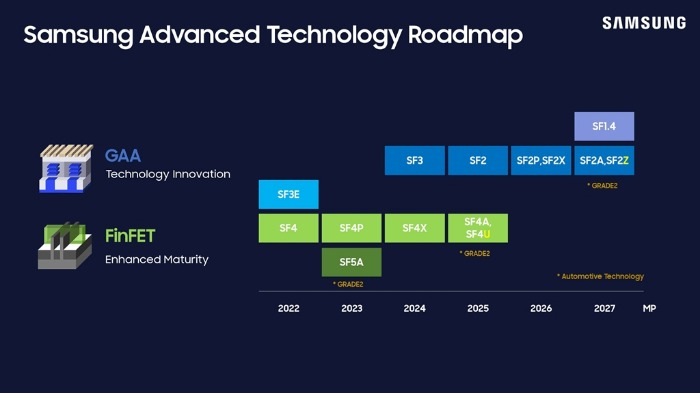

Lee also unveiled the roadmap and performance of chips to be made with the next-generation gate-all-around (GAA) technology that Samsung adopted in 2022 for the first time in the world.

It plans to mass-produce 3 nm chips based on the second-generation GAA technology (SF3) in the second half of this year and deliver GAA on its upcoming 2 nm process.

SF3 has improved chip performance and power efficiency by 30% and 50%, respectively, while reducing the chip size by 35%, compared with the chips produced on the first-generation GAA process, Lee added.

Write to Jeong-Soo Hwang at hjs@hankyung.com

Yeonhee Kim edited this article.

-

Korean chipmakersSamsung wins 2nm AI chip foundry, package order from Japan

Korean chipmakersSamsung wins 2nm AI chip foundry, package order from JapanJul 09, 2024 (Gmt+09:00)

3 Min read -

Korean chipmakersSamsung unveils new foundry tech; AI chip sales to rise ninefold

Korean chipmakersSamsung unveils new foundry tech; AI chip sales to rise ninefoldJun 13, 2024 (Gmt+09:00)

4 Min read -

Korean chipmakersSamsung, AMD to collaborate on 3 nm GAA tech chipmaking

Korean chipmakersSamsung, AMD to collaborate on 3 nm GAA tech chipmakingMay 29, 2024 (Gmt+09:00)

2 Min read -

Korean chipmakersSamsung on smooth track to 1.4 nm foundry tech to take on TSMC

Korean chipmakersSamsung on smooth track to 1.4 nm foundry tech to take on TSMCJun 28, 2023 (Gmt+09:00)

4 Min read -

Korean chipmakersSamsung to make 2-nanometer GAA chips by 2025 to overtake TSMC

Korean chipmakersSamsung to make 2-nanometer GAA chips by 2025 to overtake TSMCOct 07, 2021 (Gmt+09:00)

3 Min read